#### Graduating university:

Ministry of Education and Science of the Russian Federation

National Research Tomsk Polytechnic University

Institute of Physics and Technology

Department of Electronics and Automation of Nuclear Plants

## **Guiding Institute:**

The Academy of Sciences of the Czech Republic

Nuclear Physics Institute

Nuclear Spectroscopy Department

# Digital acquisition software and hardware for SEU chip test

By Vasily S. Mikhaylov

A graduation work

Submitted in fulfillment of the graduation work requirements for the qualification of physical engineer.

# Approved by:

Project advisor (NPI): Dr. Vasilij Kushpil

Technical consultant (TPU): Prof. S.N. Liventsov

Linguistic advisor (TPU): Dr. N.G. Novikova

Řež near Prague, Tomsk − 2013

#### **Abstract**

Achieving the sustainability of electronics against the radiation is a very important task facing the ultra relativistic physics scientists. Single event upset effect is one of the common effects which occur during the irradiation of electronics, especially SRAMs as they consist of a huge amount of transistors sensitive to the upcoming energy particles. This problem is notably significant nowadays due to the fact that the dimensions and correspondingly supply voltages of the transistors become very small and the probability that energy of ionizing particle will be enough to cause the SEU effect highly increased. The SEU effect is a very of concern for the high energy physics detectors electronics including the ALICE detector electronics used for the ultra relativistic particle investigation with LHC in CERN.

This graduation work addresses these issues related to the memory test during the charged particles irradiation. In particular, this graduation work describes simulations of SEU effect using the SPICE model of the RAM cell to predict probable level of the SEU rates. The main aim of the graduation work is to describe the hardware, the firmware and the software of digital acquisition system (DAQ) developed by Nuclear Physics Institute (NPI) Řež group used for the tests of SEU chip designed for investigation of the SEU rates and levels in electronics proposed to be used for the ALICE ITS upgrade. It is important to highlight that despite the fact that the DAQ system was developed for radiation test of SEU chip, the DAQ system is an absolutely independent complete system providing the possibility to investigate any other memory chip or other digital structure.

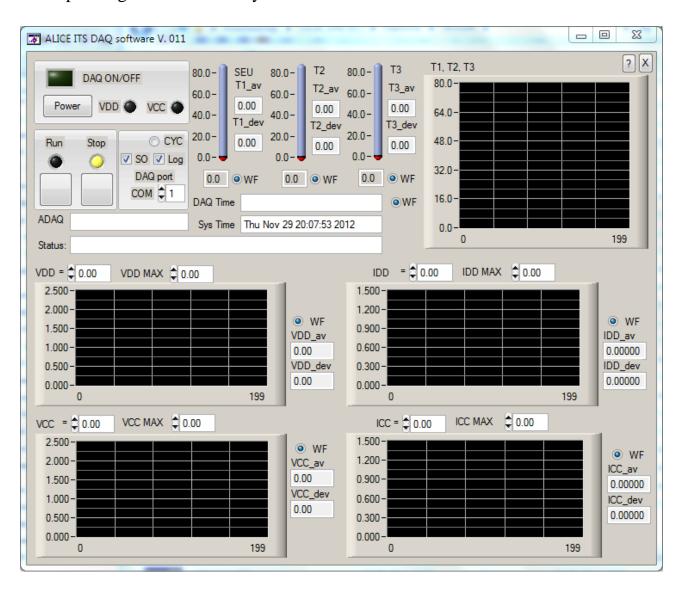

This graduation work comprehensively describes the developed DAQ hardware and its interconnections allowing processing the high-level experiments with memories or other digital structures of modern integrated circuits. The main contribution of the graduation work author is the development of the firmware and software modules, such as "SEU Test FPGA Firmware v 1.0" module allowing fast

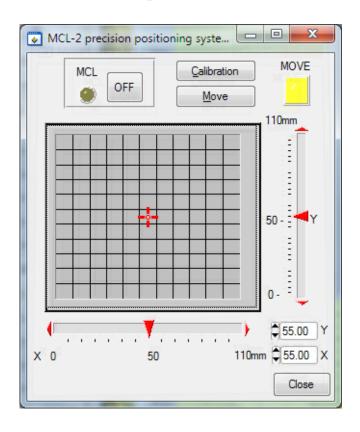

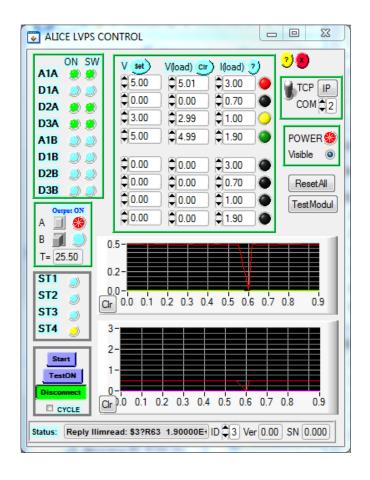

and robust FPGA operation giving the possibility to interact with SEU chip from DAQ software, the "SEU Test DAQ Software v 1.0" providing the opportunity of both analog and digital data acquisition with the help of FPGA firmware, the "SEU Test ADAQ Software v 1.0" providing the opportunity of the analog data acquisition allowing measuring the important operating parameters of the DAQ system itself, and modernization of the additional software "MCL-2 precision positioning system module" allowing control of the MCL-2 positioning hardware module and "ALICE LVPS control v 2.0" software providing the control of the LVPS module supplying the power to the whole DAQ system.

At the simulation part of the work the SPICE model of the 4T RAM cell was developed, proposed model of critical charge calculation based on additional resistor connection was discussed and expected value of critical charge resulting in the single event upset achieved for the investigated chip that is about 590pC (about 1.23\*10<sup>5</sup>MIP).

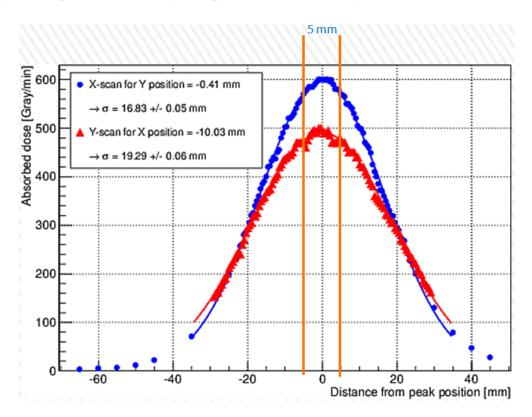

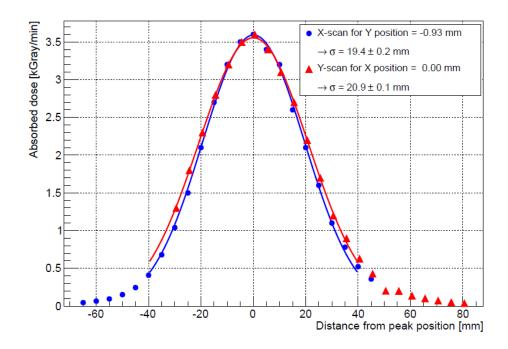

Test measurement setup of the developed DAQ system and the test results are also described in the work. During the first measurement test we prepared the necessary background to the real SEU chip test irradiation and investigated that the beam profile has Gaussian shape quite appropriate for the SEU chip irradiation. Unfortunately, during the laboratory tests of the SEU ALICE\_ITS\_TJ180\_TD\_V1 chip we investigated it has some design issues and cannot be operated, that was confirmed by the Cagliary group when they tested their own DAQ system for the SEU chip.

Here we came to the conclusion that on the one hand we need to wait for the properly designed chip to be able to acquire the data and perform next irradiation experiments with SEU chip. On the other hand we ensured that our developed DAQ system is working properly and because it is a multipurpose DAQ system we can perform the experiments with irradiation of any other memories or chips.

## Acknowledgements

I would like to express my profound gratitude to my chief Dr. Vasilij Kushpil for granting the job, giving me freedom to schedule my work time and teaching me so many things all along my work. I would also like to thank Dr. Vladimir Wagner for getting me into the Nuclear Physics Institute, resolving so many documental issues and providing much help while I was staying in foreign country. Also I want to thank Dr. Jozef Ferencei who helped me much with communication with other staff and students working in the department and for the help with solving financial and organizational issues for our project experiment. I would like to thank Josef Špalek who helped us with the measurement setup tuning and provided the LVDS board with 4m cable connection of the DAQ to SEU PCB board.

I express the great gratitude to Dr. Michal Šumbera for employing me and granting the good financing source both for my personal needs and for required project equipment. I am very grateful to Dr. Svetlana Kushpil for the very nice welcome and provision of information about different facilities in Czech Republic. I am saying great thanks to the head of my department and my university supervisor Prof. Sergey N. Liventsov for additional financial support and making this internship research possible. Finally I am very thankful for everyone I worked and communicated with during this work at Nuclear Physics Institute of ASCR.

Last but surely not least, I am indebted to my mother for endless care and support throughout my internship research.

# **Table of contents**

| 1. Introduction                                                | 6   |

|----------------------------------------------------------------|-----|

| 2. SEU Effect Theory                                           | 14  |

| 2.1 Soft Error Overview                                        | 15  |

| 2.2 Soft Error Mechanism                                       | 17  |

| 2.3 Single Event Upsets in Integrated Circuits                 | 20  |

| 3. SPICE RAM Cell Critical Charge Simulation                   | 24  |

| 4. DAQ Hardware                                                | 32  |

| 5. DAQ Firmware                                                | 40  |

| 5.1. FPGA Firmware                                             | 40  |

| 5.2. MCU Firmware                                              | 48  |

| 6. DAQ Software                                                | 55  |

| 6.1. Digital DAQ Software                                      | 56  |

| 6.2. Analog DAQ Software                                       | 66  |

| 6.3. Additional Software                                       | 71  |

| 6.3.1. MCL-2 Positioning System Software                       | 71  |

| 6.3.2. LVPS Control Software                                   | 73  |

| 7. Measurement Setup and Memory Chip Tests                     | 79  |

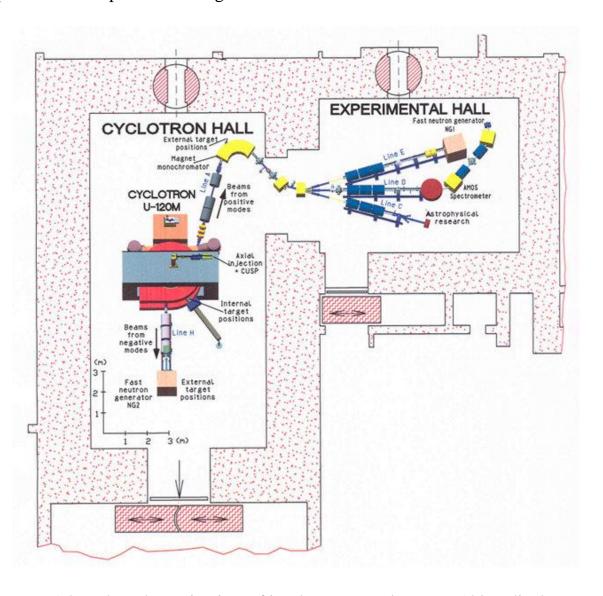

| 7.1. U-120M NPI Řež Cyclotron Facility                         | 79  |

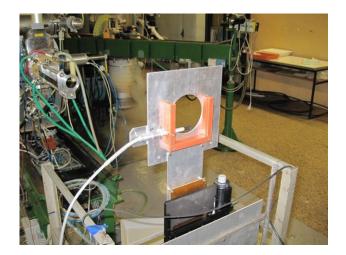

| 7.2. Test Measurement Setup and Beam Profile Scan at Cyclotron | 81  |

| 7.3. Testing of the SEU Chip Operation                         | 88  |

| 8. Conclusion and future work                                  | 93  |

| Appendices                                                     | 97  |

| A. Supplementary Hardware Description                          | 97  |

| A.1. ALICE_ITS_TJ180_TD_V1 Test Chip                           | 97  |

| A.2. LVP/S Power Supply System                                 | 102 |

| A.3. MCL-2 Precision Positioning System                        | 104 |

| A.4. UNIDOS Dose/Rate Meter                                    | 106 |

| B. Full schematic of "SEU Test FPGA Firmware v 1.0"            | 108 |

| References                                                     | 109 |

#### 1. Introduction

This chapter describes the main reasons for soft error problem in modern chips and explains general causes why the number of soft error rate in chips grown during last decades. The chapter shortly discuss the effort of ALICE Nuclear Physics Institute (NPI) Řež group ALICE ITS upgrade and denotes the resulting reliability development of DAQ system for the tests of digital structures used in particle pixel detectors, thereby outlining the motivation behind this research.

During the last thirty years the radiation influence on electronic circuits become very important task for scientific research. These studies are extremely vital due to the fact that nowadays electronics consist of very small structures such as transistors which are very susceptible even for little doses of radiation.

As it is postulated by the Moore's law the electronic chips technologies scaling decreased in quite a reasonable proportion from the end of the previous century till the beginning of current century. It especially affected the area of integrated circuits where the semiconductor technologies can be considered as a breakthrough in terms of device workability. The number of semiconductor transistors which make up the chips is doubled in each new technology generation that usually takes place in every three years. Of course, other chip operating parameters get better as well, in particular operating frequency enlarged by 44% and energy consumption used for transistor switching decreased by 65% [1Error! Reference source not found.].

Also the price per transistor on a chip has dropped dramatically since Intel was founded in 1968. Some people estimate that the price of a transistor is now about the same as that of one printed newspaper character. It looks really amazingly that nowadays average transistor gate length is about 32 nanometers while more than 60 million 32nm transistors could fit onto the head of a pin [2]. But all these advantages

and benefits of extremely small sized transistors usage has its down side expressed in different quality and reliability issues that can presently be very crucial. For example, sub-100 nanometer integrated circuits are very sensitive to various disturbances during the operation because of shortened sizes and decreased power supply voltage levels. These disturbances can be caused by such internal operational problems of the chip as supply voltage noise, ground-level noise, signal coupling and leakage currents, by variation in chip parameters during the production such as threshold voltage, channel length and channel width or by external sources such as ionizing radioactive high energy particles [3]. The point is that internal operational problems and production problems can be eliminated or at least reduced to some reasonable level by better grounding or advanced process control, today the most difficultly solved problem is still ionizing radiation.

It is obvious that decrease of the transistors and correspondingly whole devise sizes leads to an enlarged influence of radiation effects, specifically single event radiation (SER), on the performance of science, military, space, and commercial electronics [4]. The study of radiation effects can be done in multiple ways such as analysis of total dose radiation, neutron-displacement damage, dose-rate radiation, and single event radiation. Each way assumes its own method of analysis, measurements of errors, and possibilities to elimination. While all four areas are strongly important to provide a comprehensive view of robustness of electronic devices during irradiation this work centers on the impact of single event upset (SEU) radiation.

As it has already been postulated the operational problems can be caused by internal chips sources or by external sources. This statement presumes that not only the operational or process variation problems can happen as the internal chip issue but also alpha particles can be irradiated from the chip packaging material. As external sources two sources of radiation can be considered: high energy neutrons that appear with cosmic rays and any other particles coming from the human designed high energy radiation sources such as external irradiation of protons or

alpha particle during the ultra relativistic physics experiments [5]. However, the most noticeable effect is coming from transitions of high energy particles produced in accelerators, where the particle flux density is very high.

As it was previously stated SEU research is a key reliability concern for reducing the influence of ionising radiation in digital structures used at accelerator facilities such as Large Hadron Collider (LHC) at CERN [6]. The ALICE (A Large Ion Collider Experiment) CERN Collaboration has built a dedicated heavy-ion detector to exploit the unique physics potential of nucleus-nucleus interactions at LHC energies [7]. The aim is to study the physics of strongly interacting matter at extreme energy densities, where the formation of a new phase of matter, the quark-gluon plasma, is expected. The existence of such a phase and its properties are key issues in Quantum chromodynamics for the understanding of confinement and of chiral-symmetry restoration. For this purpose, the comprehensive study of the hadrons, electrons, muons and photons produced in the collision of heavy nuclei are carried out. ALICE is also studying proton-proton collisions both as a comparison with lead-lead collisions and in physics areas where Alice is competitive with other LHC experiments.

The upgrade strategy of ALICE collaboration, recently endorsed by LHC Committee, includes a new silicon tracker with greatly improved features in terms of: determination of the impact parameter (d<sub>0</sub>) to the primary vertex, tracking efficiency, and readout rate capabilities [8]. Such a new silicon tracker will allow ALICE to measure charm and beauty production in Pb-Pb collisions with sufficient statistical accuracy down to very low transverse momentum, measure charm baryons and perform exclusive measurements of beauty production. These measurements are essential in order to understand the energy loss mechanism and thermalization of heavy quarks in the Quark-Gluon Plasma state.

The radiation levels expected for the High Luminosity (after the second long shutdown in 2018) phase impose stringent requirements on the radiation hardness of

the innermost layers of the ALICE Inner Tracker System (ITS). The yearly radiation levels expected for the innermost layer (radius=22 mm), including safety-factor of 4, are 700 krad and  $10^{13}$   $n_{eq}/cm^2$  for a collected data set corresponding to 10 nb<sup>-1</sup> Pb-Pb and 6 nb<sup>-1</sup> p-p collisions. About  $10^{11}$  interactions should be recorded at the interaction rate of about 50 kHz [8]. The ALICE detector is modified to allow the readout of all interactions. It is crucial to ensure full functionality in terms of radiation hardness especially for the innermost layer.

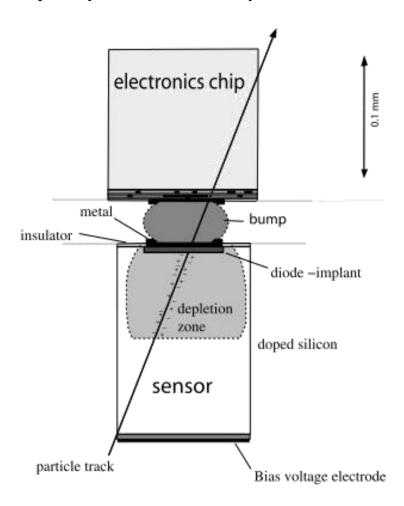

Figure 1.1 – Hybrid technology pixel detector during the irradiation

Two general technological approaches for the new particle detectors are now considered for the ALICE ITS upgrade: new monolithic pixel technology where the CMOS chip readout system is internally combined with the detector layer itself and well known hybrid pixel technology where the readout chips are connected to detector part by metal bump bonds [9]. In both technological approaches the impact of the single upset events is a very crucial concern requiring the comprehensive

testing and analysis. The influence of the high energy particles can be easily illustrated using the well known hybrid technology pixel detector during the irradiation shown at figure 1.1. In this case the charged particle goes through the device starting from its sensor part and continuing in the metal bump and then in the readout electronics chip as shown by the particle track line. In the sensor part the particle goes through the depletion zone of doped silicon layer creating the cylindrical track of electron-hole pairs with a small radius less then a micrometer and a very dense concentration of charge carriers. Then due to potential difference between the bias voltage electrode and the insulator the created carriers travel to the diode implant where they are collected and transformed to regular electrical signal and go through the bump to the readout electronics chip. But if a particle after going through the sensor part still has a viable energy it can cause the single event upset described in chapter two inside the readout chip and cause the data damage.

To simulate the impact of the expected radiation level influence on different memories used as readout for pixel detectors in the ALICE ITS systematic irradiation tests using protons were carried out throughout 2012 and onwards on various sensor, analog and digital test structures in order to:

- study their performance, stability and annealing behavior before and after

protons irradiation as the basis for a recommendation of a technology to be chosen as

baseline for the development of future ITS prototype detectors;

- gain experience in the operation of new ITS structures under realistic operational conditions;

- provide further input for simulation studies on the expected detector

performance under upgrade run conditions.

To disentangle the various possible radiation-induced effects 3 types of structures are currently under investigation: basic structures (diodes and transistors), digital structures (RAM's and Shift Registers) and full sensor structures (including analog and digital front end electronics).

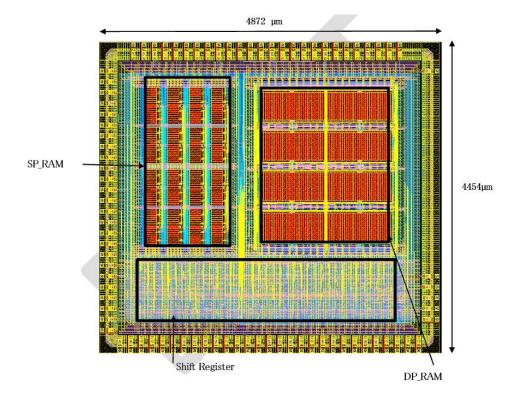

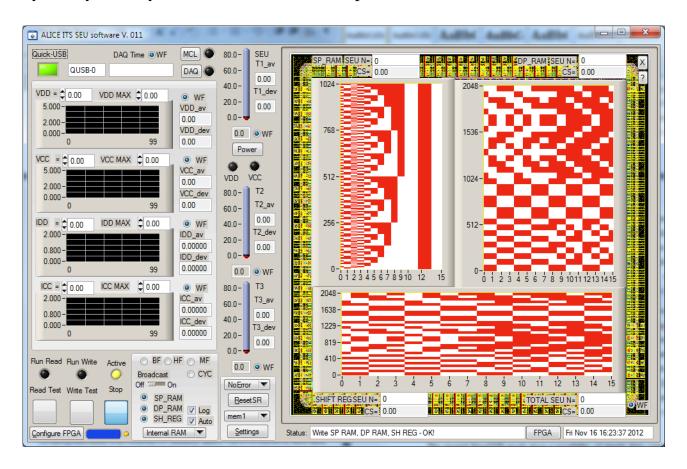

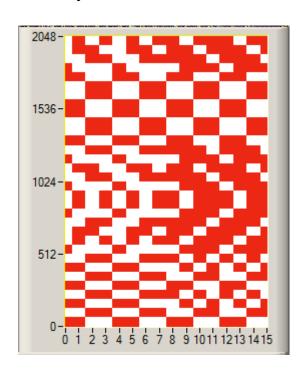

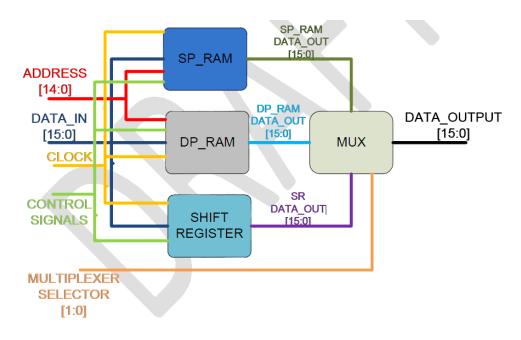

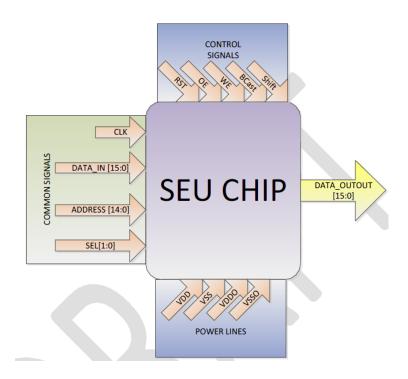

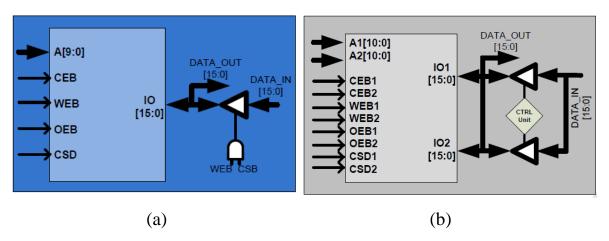

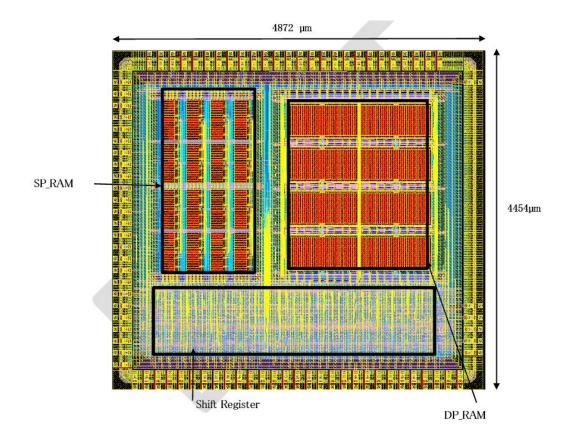

The ALICE Nuclear Physics Institute (NPI) Řež group has been a recognized and respected member of the ALICE collaboration for 20 years already. Our group was involved in a number of different ALICE projects such as development, tests and analysis of the Silicon Drift Detectors and development low voltage power supply (LVPS) system [10]. The contribution of ALICE Nuclear Physics Institute (NPI) Řež group to this effort is development of the comprehensive and robust test system for testing of the digital structures. A chip for dedicated SEU tests has been designed and implemented in TowerJazz 0.18 µm CMOS technology (SEU TJ180) consisting of [11]:

- SP\_RAM Single Port RAM block containing an array of 16 single port

RAM memories "1024@16 bits";

- DP\_RAM Double port block containing an array of 8 dual port RAM memories "2048@16 bits";

- Shift Register block with a 16 bit 32K stages.

Altogether, these structures have 81920 memory cells to test the stability and reliability of switching states during irradiation with charged particles (Figure 1.2).

Figure 1.2 – Layout of the ALICE\_ITS\_TJ180\_TD\_V1 chip

The developed test system consists of a SEU device kit board, a FPGA board for connectivity via USB and a DAQ board for the acquisition of analog data. Test measurements using this system will be carried out using mono-energetic α-sources and proton beams from a cyclotron. Dedicated software with GUI allows a convenient operation and analysis of the test data. Objectives of the test measurements are to identify the distribution of SEU across the test structures and the evaluation of the SEU cross section as a function of proton energy. The mapping of SEU can also be measured using picosecond infrared lasers.

As mentioned earlier, achieving the sustainability of electronics against the radiation is a very important task facing the ultra relativistic physics scientists. Single event upset effect is one of the common effects which occur during the irradiation of electronics, especially SRAMs as they consist of a huge amount of transistors sensitive to the upcoming energy particles. This problem is notably significant nowadays due to the fact that the dimensions and correspondingly supply voltages of the transistors become very small and the probability that energy of ionizing particle will be enough to cause the SEU effect highly increased. The SEU effect is a very of concern for the high energy physics detectors electronics including the ALICE detector electronics used for the ultra relativistic particle investigation with LHC in CERN. This graduation work addresses these issues related to a memory test during the charged particles irradiation. In particular, this work describes simulations of SEU effect using the SPICE model of the RAM cell to predict probable level of the SEU rates. The main aim of the graduation work is to describe the hardware, firmware and software of digital acquisition system (DAQ) used for the tests of SEU chip designed for investigation of the SEU rates and levels in electronics proposed to be used for the ALICE ITS upgrade. It is important to highlight that despite the fact that the DAQ system was developed for radiation test of SEU chip, the DAQ system is an absolutely independent complete system providing the possibility to investigate any other memory chip or other digital structure.

The graduation work is organized as follows. Chapter 2 provides an overview of SEU effect theory, the errors occurrence mechanism and main parameters affecting the errors occurrence. Chapter 3 proposes the basic SPICE model of RAM cell and characterizes the main parameters variations during the simulation of irradiation influence. Chapter 4 describes the DAQ hardware developed by Dr. Vasilij Kushpil for digital and analog data acquisition of irradiated digital structures. Chapter 5 reviews the DAQ firmware developed by Dr. Vasilij Kushpil and Vasily Mikhaylov for the correct and robust DAQ system operation. Chapter 6 describes the DAQ software developed by Vasily Mikhaylov and Dr. Svetlana Kushpil allowing the digital and analog data acquisition as well as simple online and offline data analysis. Chapter 7 proposes the laboratory test setup of DAQ system and the test measurement setup of this system at the NPI Řež cyclotron facility. Chapter 8 summarizes the contributions of this work and research and gives the conclusions.

#### 2. SEU Effect Theory

This chapter describes the main concerns considering the soft error effect in nanoscale chips, particularly in transistors which are used in RAMs. The chapter characterizes history and mechanism of soft errors occurrence, states the general causes why number of soft error rate in chips grew during the last decades, and identifies the main parameters substantial for SEU description.

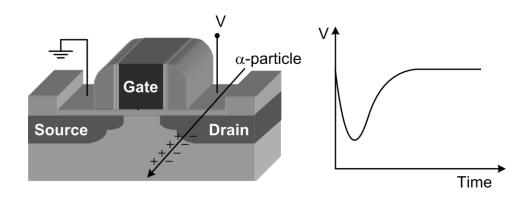

As it was described in the previous chapter the single upset event can occur when a high energy particle goes through the semiconductor electronic device. There the particle creates a dense track of electron-hole pairs along the particle track and thus produces a voltage transient at the corresponding node that collects the charge as shown at figure 2.1 [12]. This effect is also called a single event transient (SET). Reverse-biased p-n junction in transistor is the part that is most sensitive to such effects because of it is collecting charge very rapidly. It can happen that an amount of charge collected this way is enough to cause the SET which leads to a data damage in the form of flipping the logic state from high level state to low level state or other way round at the corresponding node. If such an effect occurs in one of transistors of the memory cell this event is called a single event upset (SEU). SEU effect itself does not lead to physical damage of the device and that is why it is also called "soft error".

Figure 2.1 – Simplistic view of alpha particle strike on a transistor and the resulting transient on the drain voltage [13]

Despite the fact that a "soft error" does not corrupt the chip physically, it still can cause an error for the proper chip operation and corresponding data loss. Due to the fact that energy enough for the "soft error" is much less then for the "hard error" when chip physically breaks the "soft error" rates (SER) can reach much higher limits comparing to the "hard error" rates. In a usual case hard error rates can reach 200 FIT (FIT means Failure In Time – one error per 4.54 days of chip operation) while the SER can reach up to 50.000 FIT per chip [14]. It is obvious that in radiation conditions this number increases in multiple times, so description and elimination of "soft errors" electronic chips produced with nanoscale technology is a very important point for the radiation tests and experiments.

#### 2.1 Soft Error Overview

The history of single event effects starts from the occurrence in electronics during ground nuclear experiments in 1954-1957 and space electronics tests during the 1960s [15], [16]. The first evidence of soft errors from  $\alpha$ -particles in packaging materials was reported for dynamic random access memory in 1978 [17]. Nevertheless, the soft errors did not nave any really serious influence during aforementioned times because of the big dimensions and higher power supplying voltages of electronic elements used there and provided additional protection against single event upsets such as bigger capacitance of sensitive nodes and larger noise margin.

But as it was already declared, during the time technology was scaling multiple times, while power supply voltage and capacitance of the nodes decreased by about 30% in every technology generation [18]. The decreasing of these parameters caused the decreasing in the signal charge responsible for a logic voltage level by factor two [19]. The charge which should have an ionized particle decreased because of this fact as well as because of the reduction of the chips dimensions that increased the probability of striking the node by the particle. Nevertheless the first

effect is more significant quantitatively and that is why the SER is increasing with technology scaling [20], [21].

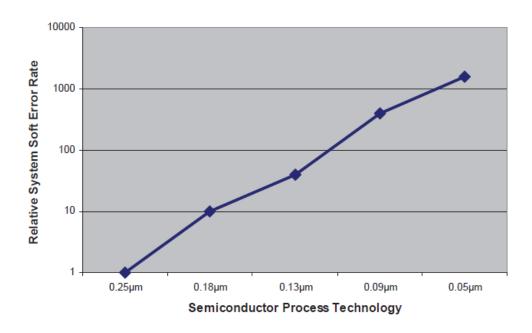

Figure 2.1 – Soft error rate prediction for the semiconductors [22]

Figure 2.1 shows the SER in semiconductor products as a function of technology process dimensions, where the data were collected by AMD, Intel, and Compaq. It is obvious from Figure 2.1 that semiconductor systems in sub-100nm technologies are very sensitive to soft errors. This results in the fact that modern microprocessor systems are developed with addition of soft error robust circuits [23], [24]. In fact, soft errors have always been a key reliability concern for mission-critical applications where a single error can lead to catastrophic failures in one case, and for severe environment applications where the heavy particle fluence lead to extremely high SER in another case. Example for the first case can be space-borne electronics or implantable medical equipment (e.g., cardiac defibrillators) while the prominent example of the second case applications is the reduction of the influence of ionising radiation in digital structures used at accelerator facilities such as Large Hadron Collider (LHC) at CERN.

#### 2.2 Soft Error Mechanism

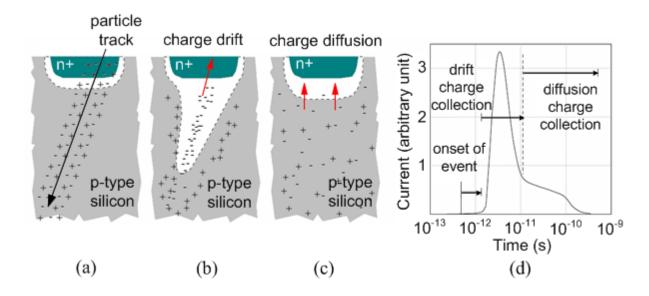

The aforementioned SEU mechanism itself can consists of three general phases: (a) start of the event, (b) charge drift and (c) charge diffusion [14]. As shown at figure 2.2, in phase (a) the charged particle goes through the depletion zone of doped silicon layer creating the cylindrical track of electron-hole pairs with a small radius les then a micrometer and a very dense concentration of charge carriers. The particle's linear energy transfer (LET) indicates the energy deposited per unit path length as a particle goes through the material and defines the amount of the charge created by the particle.

Figure 2.2 - a-c) Charged particle hit causing loss of charge in reverse-biased p-n junction, d) the transient of current at corresponding node due to the particle hit [14]

Generally, LET is defined by the energy deposition per unit length and calculated in MeV/cm and depends on the target material properties, but it can also be recalculated in the form where it becomes independent from the material properties, especially from its density with the help of dividing by the density  $\rho$  in mg/cm<sup>3</sup> (for silicon  $\rho = 2.33$  g/cm<sup>3</sup>) and presented in the MeV-cm<sup>2</sup>/mg [12]. It is possible to get the particle's charge loss per unit path length from the particle's LET, for example an LET of 97 MeV-cm<sup>2</sup>/mg is equal to a charge loss of 1 pC/ $\mu$ m in silicon. Accordingly,

the energy deposition value can be calculated from the known LET using the following formula in MeV [25]:

$$E_{dep}$$

[MeV]=LET[MeV\cm^2/mg]\pi\rho[mg/cm^3]\sqrt{s}\_{max}[cm]

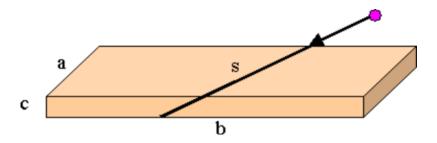

In this formula s is a path length  $s_{max}^2[cm] = 2L^2 + c^2[cm]$  for device dimensions width and length a=b=L and c – device depth as shown at figure 2.3. Of course if particle hits material at an angle its past is upgraded corresponding to the cosine law divided by cosine of corresponding angle  $cos(\Theta)$  and so forth.

Figure 2.3 – Simplistic 3D view of the device hit by charged particle.

In phase (b), electron-hole pairs generated during the particle penetration of silicon are quickly collected on the corresponding sides of the p-n junction because of the intensive electric field inside of depletion region [13]. Accordingly, holes travel to p-substrate that has the low potential while electrons travel to n-diffusion that has the high potential during the tens of picoseconds. Generated negative charged particles are increasing the depletion region during this phase as shown at figure 2.2(b) to the cone shape extending the charge collection volume where the size of the cone shape is inversely proportional to the substrate doping.

In the last phase (c) the depletion region returns to the normal size and the residual charged carriers continue travelling to the corresponding nodes of p-n junction due to the regular diffusion mechanism. This process runs on until all the remained particles are collected or recombined with each other and can take up to few nanoseconds.

At figure 2.3(d) the transient of current at corresponding node due to the particle hit is represented. The amount of charge that is collected during the current transient and called collected charge  $Q_{coll}$  can be approximately calculated by the following formula [25]:

$$Q_{coll}[C] = \frac{E_{dep}[eV] \Box q[C]}{W_{EHP}[eV]}$$

In this formula q is the initial charge of the penetrating particle, for example for electron  $q_e = 1.6022 x 10^{-19}$  C, and  $W_{EHP}$  is the energy required for the electronhole pair creation, for example for Silicon  $W_{EHP} = 3.6 eV$ .

Actually, the collected charge  $Q_{\rm coll}$  cannot be calculated so simply and depends on multiple factors, such as device's dimensions, structure of substrate and doping, variation of nodes biasing, type, energy and trajectory of the particle, the point where particle penetrated the device and the state of the device before the penetration. Of course, the  $Q_{\rm coll}$  value is inversely dependent on the distance between the node and the point where the particle started the device penetration. Also, it should be taken into account that nodes in modern cells are placed quite near to each other, so when the particle hits one of the nodes it can also touch the another nearest one and result in formation of temporary bipolar transistor between nodes that will cause the increased probability of big charge collection. Correspondingly, the bigger the collected charge is for the investigated p-n junction, the bigger is the probability of soft error happening and if the charge is ever much bigger even the hard error damaging the device can occur.

The fact that the cell collected some  $Q_{coll}$  charge lead to a single error upset event only if it outreaches a critical charge  $Q_{crit}$ , that is correspondingly defined as the minimum collected charge leading to the change of the cell state ("1" to "0" or vise versa) [12]. But if the collected charge is smaller than the critical charge calculated for this cell, the single event will not happen and the cell will remain its data properly. Accordingly, the critical charge can be considered as the main quantitative

parameter describing the ability to withstand the radiation flow for the certain investigated memory cell. For example, for the device with L x L dimensions, the critical charge causing the flip of the data state depends on the squared feature size  $(Q_{crit} \sim L^2)$  and can be calculated by the following empirical formula [26]:

$$Q_{crit}[C]=0.023[pC/\mu m^2]\square L^2[\mu m^2]$$

Thus, using the aforementioned formulas we can get the formula that describes the possible value of the threshold  $LET_{thr}$  for the irradiating particles that the investigated cell can withstand:

$$LET_{thr} \left[ \frac{eV}{mg \Box cm^{2}} \right] = \frac{Q_{crit} \left[ C \right] \Box W_{EHP} \left[ eV \right]}{q \left[ C \right] \Box \rho \left[ mg/cm^{3} \right] \Box s_{max} \left[ cm \right]}$$

For example, for the APEX FPGA the LET<sub>thr</sub>  $\approx 100 \text{ keV/mg/cm}^2$  while the LET during irradiation by the 30 MeV protons in Silicon = 15 keV/mg/cm<sup>2</sup> [27]. However, the critical charge and correspondingly LED are not constant during the different tests and for the different cells of the device because the way how the device reacts to the particle hit is described by the transient pulse form, and depends not only on the magnitude but on the temporal characteristics of the pulse as well [14], [19]. Accordingly, it is quite difficult to make the precise calculation or model of the critical charge  $Q_{crit}$  because it depends on the node capacitance and supplying voltage as well as on the restoration functions of corresponding nodes.

# 2.3 Single Event Upsets in Integrated Circuits

Due to the fact, that different types of integrated circuits can be influenced by the irradiation we will shortly review how the simple logic circuits and various memories are influenced by the ionized particles causing the single event upsets. Memories can be both dynamic random access memory DRAM and static random access memory SRAM. It is obvious, that logic circuits, DRAMs and SRAMs have different structure and that is why they should withstand irradiation differently.

Charged particles can hit the combinational logic elements and can be latched by some of them. But usually the ionizing particle hit does not cause the single event upset because of three so called masking effects: logical masking, electrical masking, and latching window masking, which unavoidably exist in sequential logic circuits [19]. The elements of logic circuits (latches or register cells) are generally less influenced by the single events in comparison with SRAM, because the transistors used in these elements are much bigger then transistors used in SRAMs and correspondingly the capacitance and operating voltage is higher for them, that leads to the higher Q<sub>crit</sub> required for the soft error occurrence.

As it was stated, both DRAM and SRAM memories are more susceptible to soft errors, in comparison to logic circuits, because they have tighter packing density that mean smaller transistors and smaller required critical charge to cause the event, and also memories do not have masking mechanisms like for the logic circuits. It means that when a charged particle penetrate the cell or number of cells are situated nearby, it will change the state of the cells with relatively high probability and this corrupted data will remain until the moment when it is rewritten.

Nowadays in DRAM signal charge is stored in 3D trench capacitors with the smaller junction volume and quite the same corresponding node capacitance comparing to the SRAM. Also it is important to note that the DRAM cells are quite frequently refreshed that works like a simple built-in error correction mechanism. This fact means that the system built on the DRAMs soft error rate is kept on almost the same level through the DRAM generations because the reduction of the SER is increased with approximately the same speed as memories packing density increases.

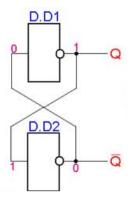

The SRAM cell is constructed by two cross-coupled inverters and stores the written data as long as the power supplying voltage is on, so it does not need any

refreshing and does not have any built-in error-correction mechanism in comparison with the DRAM cell as shown at figure 2.4.

Figure 2.4 – Two cross-coupled inverters comprising the simple memory cell

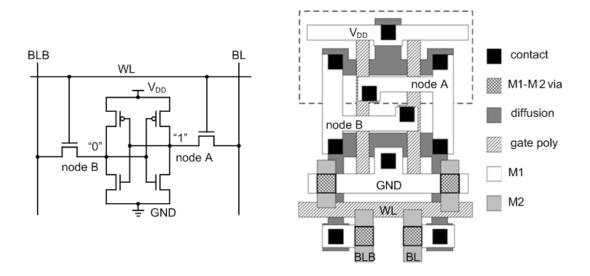

The SRAM memory is named static RAM exactly because the inverters each consisting of one NMOS and one PMOS transistor are driving each other and keep the written data bit for all the operational time until they are rewritten. The SRAM memory cell represented at figure 2.5 consist of four transistors in the center used for the data storing and the two transistors on the left and on the right used to provide the access to the cell. Due to the fact that only two transistors from the four central ones are turned ON during the operation, corresponding to the stored value, the two transistors which are OFF are very sensitive to the particle hits and thus to single event upset, particularly at their p-n junction regions.

Figure 2.5 –Six-transistor SRAM cell electronic schematic and layout.

WL: word line, BL: bit line, BLB: complementary bit line.

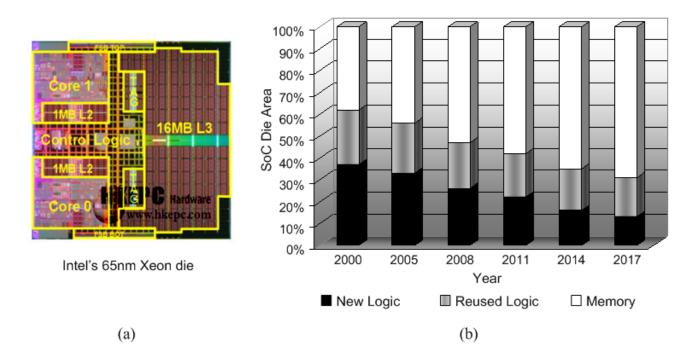

Actually, SRAM nowadays can be easily integrated with logic circuits, it does not require any special refreshing mechanisms and has quite a rapid operating, that is why it becomes the mainly used element for the embedded memory construction, that fill the most of the die area in Systems on Chip (SoC) as it is shown at figure 2.6(a) [13]. Moreover, the area of the die used for the embedded memory placement continues increasing to provide the better performance as shown at figure 2.6(b).

Figure 2.6 – a) Intel's 65nm Xeon processor die; b) forecast for the memory area trend on SoC die (Semico Research Corp.).

Summarizing the aforementioned information, we can say that nowadays SRAM single event upset sustainability is considered as the most important parameter for the whole System on Chip due to the fact that SRAM occupies the most of the die area and is the most sensitive element of SoC from the SEU sustainability point of view. Due to this fact the task of investigation of SRAM used for the particle detectors readout systems sustainability against the ionizing radiation in hard radiation conditions such as the ultra-relativistic particle physics experiments become very important today.

#### 3. SPICE RAM Cell Critical Charge Simulation

This chapter presents the brief review of SPICE simulation system, comprehensively describes the SPICE model of the 4T RAM cell and represents the results of simulation.

The simulations of the critical charge is very important nowadays for all the memory chips used in radiation conditions. For example, the advent of circuit simulators, including PREDICT, ECAP, NET-1, CIRCUS, SPICE, and SCEPTRE, was directed, at least in part, by the need to model radiation effects in circuits [28], [29].

Micro-Cap 10 is an integrated schematic editor and mixed analog/digital simulator that provides an interactive sketch and simulate the environment for electronics engineers. Micro-Cap 10 blends a modern, intuitive interface with robust numerical algorithms to produce unparalleled levels of simulation power and ease of use. Familiar SPICE models are easy to be applied with the Micro-Cap 10 [30].

SPICE is a general-purpose circuit simulation program for nonlinear dc, nonlinear transient, and linear ac analysis. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, lossless and lossy transmission lines (two separate implementations), switches, uniform distributed RC lines, and the five most common semiconductor devices: diodes, BJTs, JFETs, MESFETs, and MOSFETs [31].

This system of the cell construction and simulation was chosen due to the fact that it allows easy and robust development and edition of the electronic circuits as well as descriptive and adjustable transient and dc analysis of the developed circuit.

The first step of the 4T cell model development and simulations is to achieve the parameterized model of the single NMOS and PMOS transistors which should agree with the transistors used in the SEU chip. The Schichman-Hodges Model for the n-channel metal—oxide—semiconductor field-effect transistor (MOSFET) or

NMOS was used because it fully satisfies the requirements for the needed characteristics of transistors used in SEU chip.

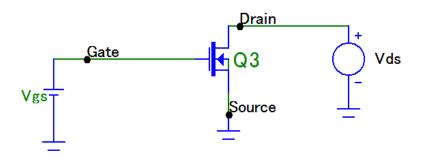

Using the NMOS with the chosen model the following schematic was developed to obtain the parameter-depended transistor characteristics shown at figure 3.1. In scheme the Gate terminal is connected to the voltage source Vgs to form the opening voltage for the transistor Q3. The Drain terminal is connected to the voltage source Vds to from the current going through the transistor from the Drain terminal to the Source terminal.

Figure 3.1 – Schematic of the NMOS connected to two voltage sources

The main parameterized function for NMOS model characterizing its properties is dependence of the drain-source current  $I_{ds}$  on the drain-source voltage  $V_{ds}$  with different constant gate-source voltages  $V_{gs}$ . In the Schichman-Hodges Model the function of  $I_{ds}$  depends on multiple transistor parameters according to the following formula divided into three regions of  $V_{ds}$ :

$$\begin{split} I_{ds} &= 0.0 \text{ , } V_{gs} \leq V_{th} \text{ ;} \\ I_{ds} &= KP \Box \frac{W_{eff}}{L_{eff}} \Box (1 + \lambda \Box V_{ds}) \Box (V_{gs} - V_{th} - \frac{V_{ds}}{2}) \Box V_{ds} \text{ , } V_{ds} < V_{gs} - V_{th} \text{ ;} \\ I_{ds} &= KP \Box \frac{W_{eff}}{L_{eff}} \Box (1 + \lambda \Box V_{ds}) \Box (V_{gs} - V_{th})^2 \text{ , } V_{ds} \geq V_{gs} - V_{th} \end{split}$$

where KP [A/V²] is intrinsic transconductance parameter,  $W_{eff}$  [µm] is effective gate width,  $L_{eff}$  [µm] – is effective gate length,  $\lambda$  [V¹] – channel-length modulation,  $V_{th}$  – zero-bias threshold voltage.

Value of KP is calculated by the following formula:

$$KP = UO \square C_{ox}, C_{ox} = \frac{\varepsilon_{ox}}{T_{ox}} \Rightarrow KP = UO \square \frac{\varepsilon_{ox}}{T_{ox}}$$

where UO [cm<sup>2</sup>/(V·s)] is surface carrier mobility,  $C_{ox}$  [F/cm<sup>2</sup>] is oxide capacitance per unit gate area,  $\epsilon_{ox}$  [F/cm] – is oxide permittivity,  $T_{ox}$  [cm] – gate oxide thickness.

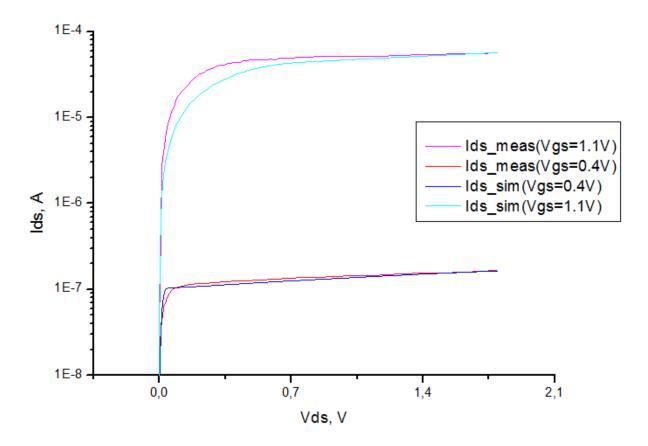

For both regions of  $V_{ds}$  the values of parameters used for the  $I_{ds}$  calculation were tuned to achieve the required form of  $I_{ds}(V_{ds})$  function given by producer's measurements [32]. The following values and parameter variation range were determined in the producer's presentation:  $W_{eff} = 0.22 \mu m$ ,  $L_{eff} = 0.18 \mu m$ , constant Vgs = 0.4V; 1.1V and variation of Vds in range from 0.0V to 2.1V [32]. The rest parameters were tuned in order to satisfy the producer's requirements as follows:  $\lambda = 0.35 \text{ V}^{-1}$ ,  $V_{th} = 0.36 \text{ V}$ ,  $UO = 90 \text{ cm}^2/(V \cdot s)$ ,  $\varepsilon_{ox}$  (SiO<sub>2</sub>) = 3.9· $\varepsilon_{ox}$  = 3.9·8.854·10<sup>-14</sup> = 3.45·10<sup>-13</sup> F/cm,  $T_{ox} = 3 \cdot 10^{-7}$  cm,  $KP = 1.03 \cdot 10^{-4} \text{ A/V}^2$ .

Figure 3.2 – Comparison results of the simulated and measured  $I_{\text{ds}}(V_{\text{ds}})$  dependences

The direct current (DC) analysis was performed for the developed scheme shown at figure 3.1 with implemented NMOS with parameterized model based on in the afore calculated parameters. The comparison results of the simulated and measured  $I_{ds}(V_{ds})$  dependences are shown at figure 3.2. It is clear that the achieved simulated functional dependence of  $I_{ds}$  on  $V_{ds}$  quite adequately represents the  $I_{ds}(V_{ds})$  dependence measured by the chip producers. The dependences for PMOS transistor are quite similar, so they are not presented here to avoid redundancy.

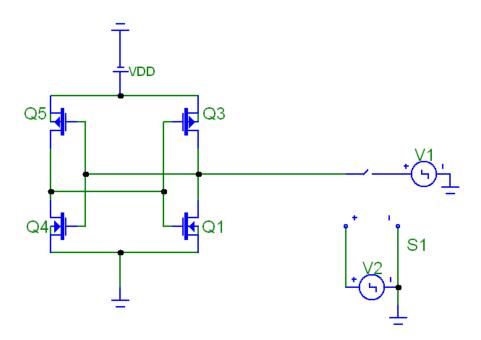

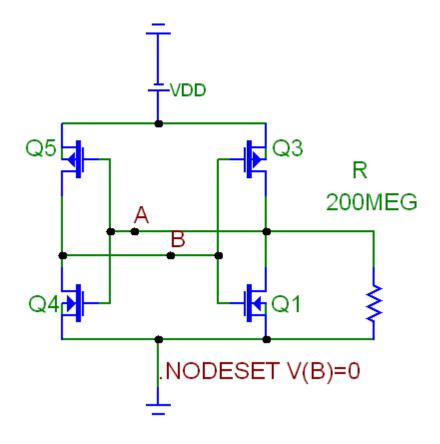

The second step of the 4T cell model development and simulations is creation of model of the 4T RAM cell operated by two impulse voltage sources in Micro-Cap 10 software. 4T RAM cell is compiled by 2 NMOS transistors Q1 and Q4 and two PMOS transistors Q3 and Q5 connected as an inverter. All four transistors employ afore described parameterized MOSFET model.VDD voltage source is used as high level voltage source supplying the regular 1V. Impulse voltage source V2 is used as access elements which enables read and write access to cell and provides isolation when the cell is not accessed. Impulse voltage source V1 is used as a writing element which writes the data bit to the cell. The schematic of the developed 4T RAM cell is presented at figure 3.3.

Figure 3.3 – Schematic of 4T RAM cell operated by two impulse voltage sources

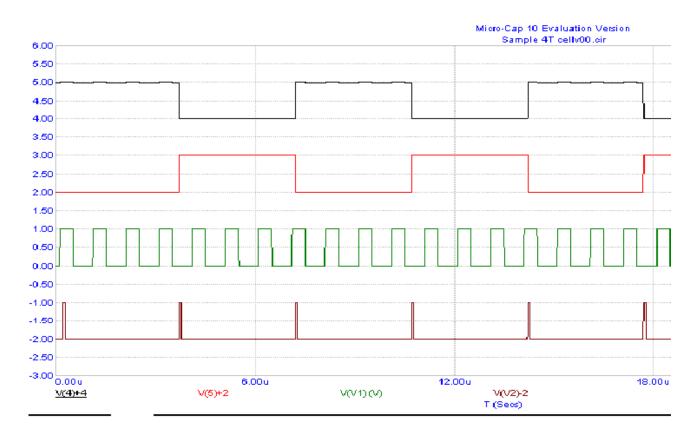

The V1 impulse voltage source has 10MHz frequency, V2 impulse voltage source has 286kHz frequency, and they are combined in the way that the value stored in cell switches with frequency 286kHz. The time diagram of the cell switching operation achieved by transient analysis is shown at figure 3.4. This figure is the evidence that the developed 4T cell model is working correctly.

Figure 3.4 – Time diagram of the cell switching operation achieved by transient analysis. V(4) – stored bit value, V(5) – inverted stored bit value, V(V1) – value of impulse voltage source V1, V(V2) – value of impulse voltage source V2

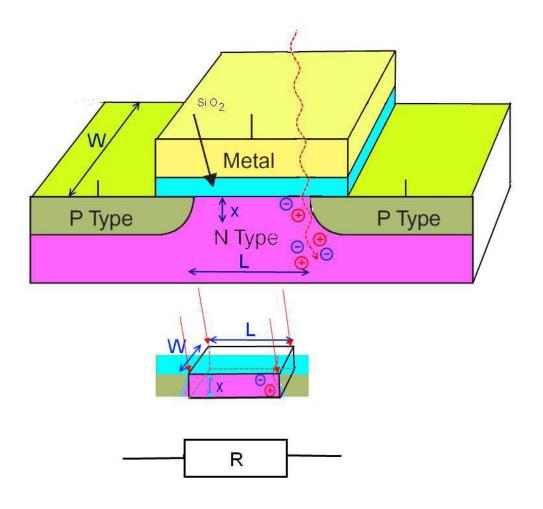

The final step of the 4T cell model development and simulations is to simulate afore described and developed 4T RAM cell model combined with the resistance used for the SEU critical charge estimation. The main idea is that if we connect an additional resistor between the drain and source nodes of one transistor, the total resistance of this triggering element will be changed as shown at figure 3.5. Using this model we can find the resistance value which forces the transistor to switch its state and therefore to switch the value stored in the cell.

Figure 3.5 – Parallel MOSFET and resistor connection changing the summary resistance

In this case the critical charge can be calculated using the following equations:

$$\begin{split} R = & \frac{\rho \cdot L}{W \cdot x}, \rho = \frac{1}{e \cdot \mu \cdot N_d} \Longrightarrow N_d = \frac{L}{e \cdot \mu \cdot R \cdot W \cdot x}, \\ x_{ON} = & \rho \cdot \frac{L}{W \cdot R_{ON}}, \end{split}$$

where  $\mu$  – electron mobility for Si,  $\rho$  – resistivity of channel,  $N_d$  – donor concentration, R – resistance of channel, W, L, x – parameters of MOSFET.

The developed model of RAM cell combined with the resistor to provide the critical value of channel resistance calculation is shown at figure 3.6.

Figure 3.6 – Model of RAM cell combined with the resistor to provide the critical value of channel resistance calculation

In this model the ".NODESET V(B)=0" function is used to define the circuit initial conditions: voltage at point B V(B)=0V and voltage at point A V(A)=1V correspondingly, due to the fact that these voltages are related inversely. With help of Transient analysis simulation we found that at the resistance R=9.80hm the cell switches its state to V(B)=1V, V(A)=0V. It means that at R=9.80hm the charge in channel of transistor Q1 becomes critical.

The investigated LVMOS transistor has the following parameters:  $\mu$ =500 cm²/(V\*s),  $N_d$ =9.298\*10<sup>15</sup>cm<sup>-3</sup>,  $R_{OFF}$ =150KOhm,  $R_{ON}$ =0.5Ohm, W=0.22 $\mu$ m, L=0.18 $\mu$ m. The value of critical charge calculated with the help of afore presented equations for 300 $\mu$ m Si is about 590 $\mu$ C that is equal to about 1.23\*10<sup>5</sup>MIP (minimum ionizing particles). This value is less than for the real process because a part of charge will recharge the output capacitance of MOSFET. We should expect the better result

from real measurement of the test structure. This method can be applied to investigate random switching of MOSFET under irradiation if MOSFET is biasing to the OFF state.

Summarizing the aforementioned information, in this chapter we have overviewed the developed SPICE model of the 4T RAM cell, discussed the proposed model of critical charge calculation based on additional resistor connection and achieved the expected value of critical charge resulting in the single event upset event for the investigated chip that is about 590pC (about 1.23\*10<sup>5</sup>MIP). It is important to note that this value is less than for the real process because a part of charge will recharge the output capacitance of MOSFET.

#### 4. DAQ Hardware

This chapter presents the detailed description of hardware devices and modules used for the research. Methods and possibilities of hardware programming and controlling are discussed as well.

Due to the complex measurement setup has been developed for the research purposes the distinctive features of individual devices should be considered to provide reliable and robust interconnection. Accordingly, in this chapter we discuss the main features and performance capabilities of the hardware used, design issues of the measurement setup integrally and operational conditions suitable for performing an experiment.

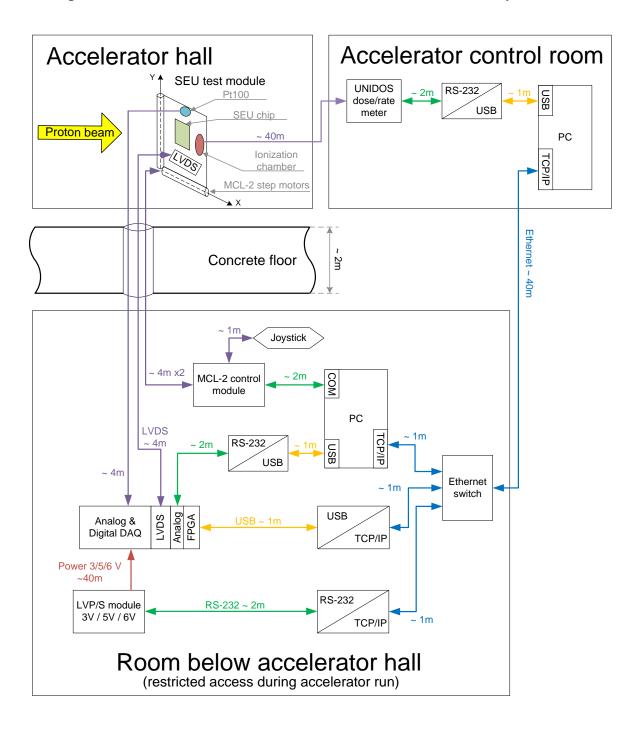

Digital and Analog Data acquisition system (DAQ) is a system, developed for the acquisition the data and controlling of the SEU chip. The system can also be used for connection to addition devices such as MCL-2 precision positioning system via RS-232 interface (see appendix A.3 for more information).

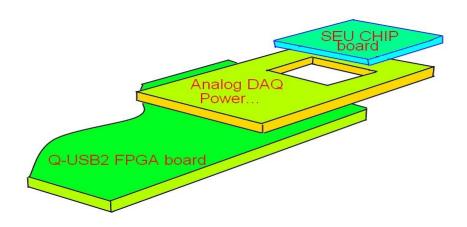

Figure 4.1 – Mechanical construction of DAQ

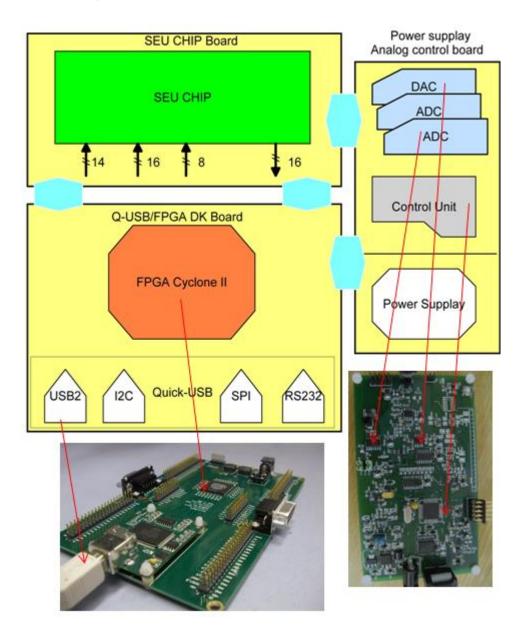

The DAQ is composed of three individual parts as shown at figure 4.1:

Digital DAQ (DDAQ) board based on Quick-USB2 FPGA Developing Kit board (QUSB) to provide digital signals delivery to SEU chip with the help of USB interface;

- Analog DAQ and power supply board (ADAQ) for controlling power supply voltages and currents as well as temperature of the SEU chip;

- SEU chip connecting board (SEUPCB) for chip package placement by standard bounding method.

The DAQ system and interconnection scheme with reference to real modules photos is shown at figure 4.2.

Figure 4.2 – Digital and Analog Data acquisition system scheme and its particular parts: Quick-USB2 FPGA Developing Kit board on the left and Analog DAQ board on the right.

The DDAQ is based on the QuickUSB Developing Kit that includes QuickUSB Cyclone II Evaluation Board and QuickUSB Module [33]. The QuickUSB module is used for the easy and reliable USB connection implementation for the DAQ system. The Cyclone II Evaluation Board has a QuickUSB module site and 0.1" headers that bring all the signals out. Altera EP2C20F256C7 Cyclone II FPGA on board contains over 1 Mbit of RAM available without reducing available logic and connects to nearly every pin of the QuickUSB module and extra I/O pins go to 0.1" headers [34].

Since the FPGA is an Altera Cyclone II, Quartus II Web Edition is used to design digital circuitry [35]. The FPGA is configured using QuickUSB libraries functions implemented inside the DAQ software described in chapter 6.1. The Starter Kit receives its power from the standard USB bus power supply as well as from power jack 5V/2A power supply on board. In addition, the I/O connectors for the QuickUSB module supply unregulated 5V and the I/O connectors for the FPGA supply regulated 3.3V. The Altera FPGA can get its clock from either the QuickUSB module (48MHz/30MHz), from a clock oscillator socket on board, and/or from a clock signal connected to the clock pin headers.

All the digital I/O and control signals for SEU chip are formed at the FPGA board. The signals are going from the FPGA external pins to QUSB-ADAQ connector pins and then to ADAQ-SEUPCB connector pins. The Cyclone II FPGA contains four integrated PLLs and one of them is used to generate 10MHz clock for the SEU chip. The same PLL is also used to provide the communication of the DDAQ board and PC in so called Full Handshake mode to synchronize the SEU chip and USB interface for operation at 10MHz. Due to the fact that regular operation frequency of USB interface is 48MHz, we need to decrease this frequency to 10MHz that can be done by Full Handshake mode operation. In this mode each cycle of data transfer via USB connection is processed when the confirmation signal appears at the corresponding Quick-USB board READY pin. So, the synchronization in our case is done by sending the 10MHz signal shifted to the 50 degrees due to the timing

requirements to the READY pin (timing requirements are described at Quick-USB user guide [33]).

The QUSB board also contains another popular serial interfaces such as I2C, SPI, RS-232 to provide external connections. In our case two RS-232 interface connectors provide auxiliary option to control the ADAQ board and/or MCL-2 precision positioning system. The control libraries are available for Windows, Linux and Mac PC operating systems [36].

ADAQ is a custom board developed in the NPI by Dr. Vasilij Kushpil to provide power supply to SEU chip, power supply parameters control such as voltages/currents and temperature control of the SEU chip itself. ADAQ consist of multiple electronic components to provide the described features. The seven TXB0108 8-Bit Bidirectional voltage-level translators with auto-direction sensing are used to convert 3.3V digital signals from FPGA to 1.8V digital signals feeding SEU chip I/O pins.

The main processing element of the board providing the control of the above described parameters as well as connection via RS-232 interface with DAQ software on PC is Microcontroller Unit ATmega32 (MCU). ATmega32 is a high-performance, low-power AVR® 8-bit Microcontroller with various components and features such as advanced RISC architecture, nonvolatile program and data memories (32kB Flash, 1024B EEPROM, 2kB SRAM), JTAG and USART interfaces, internal calibrated RC oscillator, on-chip analog comparator, 32 programmable I/O lines, etc [37]. The MCU handle all the analog signals going from ADAQ analog elements and deliver them to DAQ software via RS-232 interface and vise versa.

The power supply system is one of the most important parts of the ADAQ board. The setting of the SEU chip power supply can be implemented in two ways. The first and the best way is to use the digital-to-analog converter (DAC) paired with voltage regulators to precisely set the required voltage values from DAQ software. But there is a second "reserve" way to set the voltages values manually using

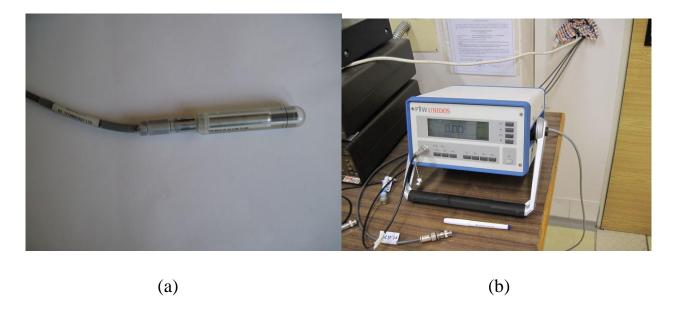

trimming resistors mounted on the board. One analog-to-digital converter (ADC) is used to provide measurement of voltages and currents of SEU chip power supply lines to ensure the proper and secure power supply. Moreover this power supply system allows estimating probable dependencies of SEU chip operation on varying the supply voltages values. Another ADC is used as safety feature paired with two resistance thermometers to ensure the secure operation of power supply of voltage stabilizers themselves concerning their temperatures. The aforementioned ADC paired with Pt-100 Platinum resistance temperature sensor with a temperature range of -200°C to 850°C is also used to control the SEU chip temperature [38]. During tests overheat can be crucial for the chip operation and PT-100 can be used to estimate probable dependences of single events accumulation on temperature.

Normally 10MHz clock signal for SEU chip operation is provided by one of three external FPGA outputs connected to the chip clock input. But as an auxiliary feature ADAQ board comprises its own separate internal 10MHz oscillator to provide independent clock source for the chip.

ADAQ board has two separated power supply lines of +5V and +3V for its own analog elements power supply and for SEU chip power supply correspondingly to avoid possible ground fault currents, leakage currents and other conditions that interfere the proper functioning of the system. The power is supplied to the ADAQ board from the LVPS module (for more information see appendix A.2).

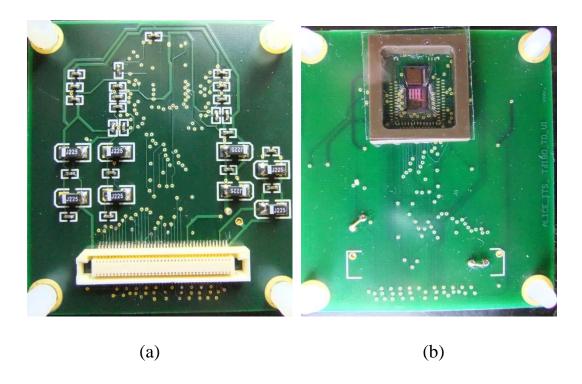

The SEUPCB is a simple small printed circuit board for connection of the chip to DAQ system without package placement by standard wire bounding method. The board is auxiliary PCB with 53x50mm dimensions and width of 1mm. The SEU chip board with all the placed elements and bonded SEU chip is shown at figure 2.2.3. The bonding of the SEU chip to SEUPCP board was done at the DESY Zeuthen bonding center with many help of Josef Ferencei [39]. The main feature of development of separate board for SEU chip placement is the possibility to place it to testing environment (proton beam) while the main DAQ system is situated in secure

place out of irradiation to ensure stable operation of its digital and analog elements. This is very crucial concern for cyclotron test because it is possible to maintain shielding versus proton beam but it is almost impossible to shield against neutron gas that exists all over the testing environment during the cyclotron operation (accumulated dose measured by dosimetry department staff is around 10mSv/h, see chapter 7.2 for more details).

Figure 4.3 – Photo of the SEUPCB chip board with all the placed elements and bonded SEU chip: a) Bottom side view; b) Top side view.

There are several options of implementation of data acquisition and control for SEU chip. The first option is the so called "slow test operation" when all the data to/from SEU chip is transferred through the developed DAQ system to the PC via USB interface. In this case all the data is processed within the DAQ software running on PC as well as the data comparison and estimation if single event happened or not. On the one hand this is the easiest option, on the other it limits the data exchange speed due to the USB speed exchange limitation. The second option is a so called "fast test operation" when general data exchange is proceeded between the SEU chip and FPGA. In this case the simple data processing algorithm is implemented inside

the FPGA. This algorithm allow the FPGA firmware to decide if single event occurred at any data cell and if so the information about corrupted data cell is transfer to the GUI running on the PC via USB interface. This option provides better data acquisition speed but requires more accurate testing and revision. The first option is already implemented to ensure the reliability of the system as a whole and the second option can be implemented to increase the data acquisition rate in future.

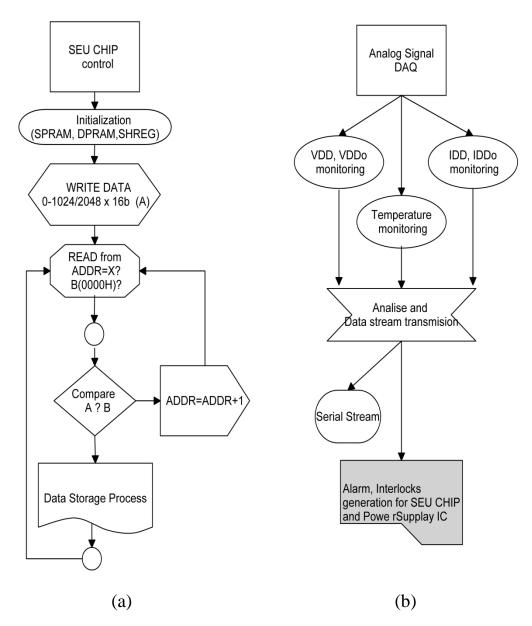

Figure 4.4 – General flowchart of hardware operation in: a) data acquisition of single events accumulation; b) SEU chip operational status and power supply control.

The embedded software and firmware is designed in the way to obtain two independent real time processes: first one to control SEU chip single events

accumulation and corresponding data exchange, second one to control the SEU chip operational status and power supply control. The flowchart of data acquisition of single events accumulation is shown at figure 2.2.4(a) and the flowchart of the SEU chip operational status and power supply control is shown at figure 2.2.4(b).

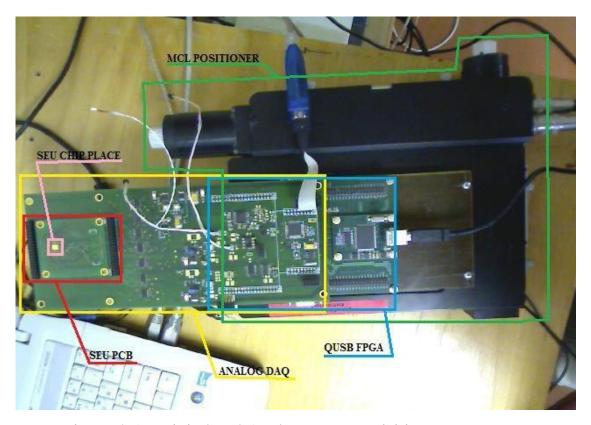

The whole DAQ system setup connected with MCL-2 precision position stepping motors is shown at figure 2.2.5.

Figure 4.5 – Digital and Analog Data acquisition system setup connected with MCL-2 precision position stepping motors

Summarizing the aforementioned information, in this chapter we have presented an overview of all the main hardware developed for the SEU chip test measurement setup. All the other hardware used in the measurement setup is shortly reviewed in appendix A. We described the DAQ system providing and delivering digital signals and power supply for the SEU chip allowing reading and writing data in/out the chip in details. Thus, this chapter has provided the necessary background on hardware and its interconnections and states the necessity of usage of all the devices, paving the way for the following chapters.

### 5. DAQ Firmware

This chapter provides the comprehensive description of developed DAQ firmware operation principles. The chapter discusses in details two independent firmware modules developed for this purposes, expounds the connection of firmware with DAQ software and reveals the hardware signal connections inside the DAQ board.

Due to the fact that two independent channels for digital and analog data acquisition are used, two firmware modules were developed to operate these channels. The first firmware module "SEU Test FPGA Firmware v 1.0" is designed to operate the digital data acquisition driving the FPGA module while the second firmware module "SEU Test MCU Firmware v 1.0" is designed to operate the analog data acquisition driving the microcontroller. The both modules are independent program components not relying on each other, but in complex allowing the trustworthy regular DAQ system operation.

#### **5.1. FPGA Firmware**

The "SEU Test FPGA Firmware v 1.0" module was designed to be implemented with FPGA of QuickUSB board reviewed in chapter 4. The module was developed in the Altera Quartus II Web Edition software as a Block Diagram with multiple VHDL\* block functions because this is the primary supported software by Altera company for all the Cyclone devices family. The reason for choosing the Block Diagram structure is the possibility of development of complex modifiable firmware that is perfectly suitable for SEU test and can be easily modified for other purposes. This firmware is one of the main contributions of this graduation work author to the SEU measurement setup which means that it was developed by Vasily Mikhaylov.

<sup>\*</sup>VHDL (very-high-speed integrated circuits hardware description language) is a hardware description language used in electronic design automation to describe digital and mixed-signal systems such as and integrated circuits [40].

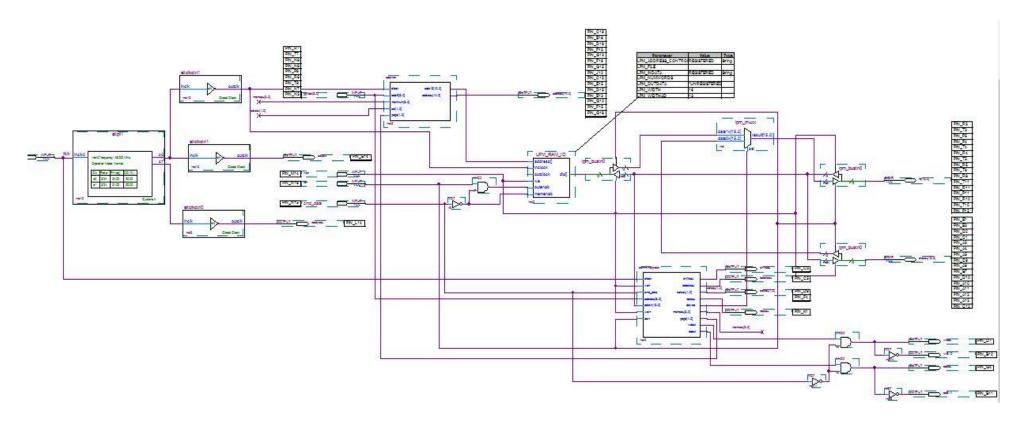

Figure 5.1.1 – General schematic of the FPGA firmware and its interconnection with other modules

The general schematic of the FPGA firmware and its interconnection with other modules are presented at figure 5.1.1. The FPGA firmware communicates with the DAQ software via the Quick-USB module, so Quick-SUB module receive the data and commands from the PC via USB bus and transferring it to FPGA via dedicated FPGA input pins. The FPGA returns the required signals to its output pins, then they go through the DAQ board to the Level converters converting the voltages levels from 3.3V to 1.8V. The converted 1.8V signals are transferred to the SEU PCB or another auxiliary board via the LVCMOS LVDS receiver-transmitter pair and then feed the SEU chip or another memory/chip connected at its auxiliary board. The detailed description of the individual modules is given in the following text.

Due to the architecture, design and programming features of QuickUSB device the signals from DAQ software are going to the FPGA in two different ways.

General data transfer signals such as clock, write enable, read enable, 9bit address and 16bit data signals have they own dedicated pins and simply pass to the FPGA internal pins from the QuickUSB board. Other signals important for the FPGA operation but not having dedicated pins are transported by special so called "command line" used for transferring user defined commands to FPGA. In fact, the commands are transferred to FPGA using the same general data line when cmd\_data signal is HIGH. Accordingly, regular data transfer is processed when cmd\_data signal is LOW. The usage of programming features allowing described data transfer with the help of DAQ software is presented in chapter 6.1.

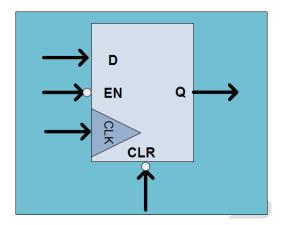

Figure 5.1.2 – The "Addriner" function block schematic

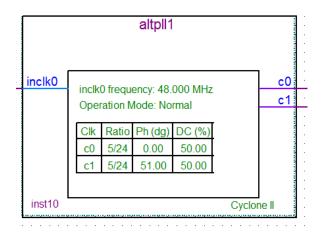

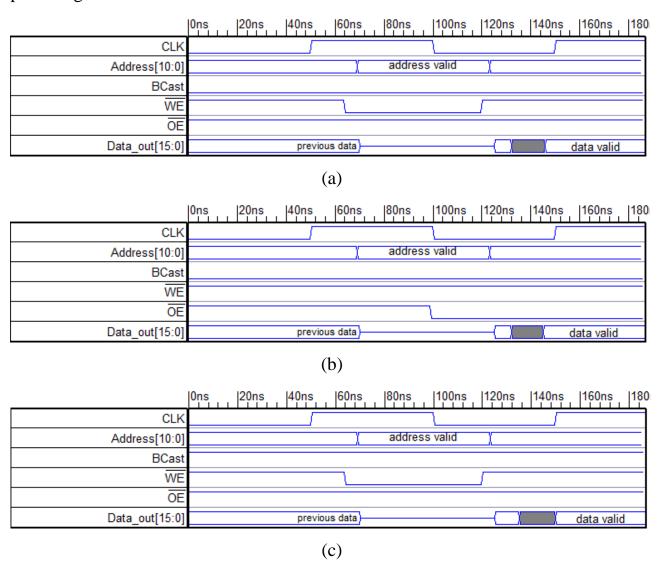

As it was described in chapter 4 SEU chip has 16bit data line, 15bit address line and control signals: CLK, SHIFT, BCAST, SEL and RESET required for proper operation. The 10MHz clock signal CLK for the SEU chip is generated in the FPGA's PLL from the 48 MHz QuickUSB board clock and is directly feeding the SEU chip input. This PLL is also used to form another 10MHz clock phase shifted from first one to 51 degrees due to usage of Full Handshake QuickUSB operation mode requirements described in chapter 4.1. The schematic of "altpll" function block generated from ALT\_PLL megafunction to operate the FPGA's PLL is shown at figure 5.1.2.

The 16bit data line of SEU chip is directly connected to external 16 bit bidirectional data line of FPGA using the parameterized tri-state buffer generated

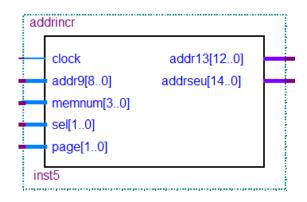

from lpm\_bustri Megafunction. But there is another situation regarding the address line of SEU chip due to the dimensions of address lines are different: the QuickUSB address line consists of 9bits and SEU address line consists of 15 bits, so they can not be directly connected to each other. This problem is solved by increasing 9 bit address line with the help of command data line in VHDL-module "Addrincr". The 9 less significant bits are transferred by the general QuickUSB address line while rest 6 bits are transferred via command line then all the address bits are added together inside the "Addrincr" to form the required 15 bit address line (addrseu[14.0])feeding the SEU chip (memnum[3..0] + page[1..0] + addr9[8..0]). This function is currently used to form the 13 bits address (addr13[12..0]) for virtual RAM which consists of 10 less significant bits (page[1..0] + addr9[8..0]) to simulate address of one RAM block and 2 rest bits (sel[1..0]) to choose between virtual SP\_RAM and DP\_RAM. The schematic of "Addrincr" function block working on 10MHz clock from PLL to ensure the synchronous operation with virtual and SEU chip RAMs is shown at figure 5.1.3.

Figure 5.1.3 – The "Addriner" function block schematic

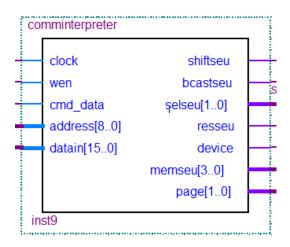

Another important VHDL-function developed for the realization of connection between the DAQ software and FPGA firmware using general and command data transfer is the "Comminterpreter" function used for the interpretation of commands sent from DAQ software on PC to FPGA firmware. This function exploits standard "Case" structure to distinguish different commands using the general address bits as comparison parameter and the general data bits as the

transferred value. Each command has its unique 9 bit address defined in the "Comminterpreter" function as well as in DAQ software to avoid any command interpreting mistakes. This function is processed using the 48MHz USB clock for the command processing speed increasing and only when write enable (wen) and cmd\_data signals are HIGH to ensure the fact of working with command line. In particular, such parameters as SHIFT (shiftseu), BCAST (bcastseu), SEL (selseu[1..0]) and RESET (resseu) assigned to the SEU chip input parameters as well as additional MEMSEU[3..0], PAGE[1..0] and DEVICE designed for internal FPGA usage are transferred via command line using "Comminterpreter" function. The SEU chip input parameters are described in appendix A.1 while MEMSEU and PAGE signals are used to form the RAM address and DEVICE command signal is used to switch between the virtual and the SEU chip RAM. The schematic of "Comminterpreter" function block is shown at figure 5.1.4.

Figure 5.1.4 – The "Comminterpreter" function block schematic

The developed firmware can operate in two principally different regimes – Internal RAM Simulator and External RAM Connection. The Internal RAM Simulator regime allows user to read/write data of the virtual RAM internally simulated in the FPGA module. This virtual internal RAM is absolutely identical in terms of addressing and data storage to the RAM of the SEU chip described in appendix A.1. General purpose of virtual RAM is to provide the opportunity of online test of measurement setup to ensure its operability in case of bad responses from

SEU chip as well as off-line test of measurement setup while the SEU chip is not connected. Virtual RAM can also be used in the following Firmware version upgrade as one of the parts providing the "fast test operation" described in chapter 4.2. The External RAM Connection regime is used when the SEU chip is connected allowing the direct manipulations with its memories. In this regime all the data goes from DAQ software on PC through the FPGA to the SEU chip input pins bypassing any internal FPGA usage or conversions. The switching between the virtual RAM and SEU chip RAM is done by multiplexing of the data flows from the RAMs to DAQ software by multiplexor connected to the DEVICE regime switching signal sent from the GUI. The multiplexing of the data flows going to the RAMs is done just by multiplying of DEVICE signal to the write enable signal of the corresponding memory (it is also important to mention that the cmd\_data signal is multiplied to write enable and output enable signals going to both memories to ensure that they are not accessed during command transfer).

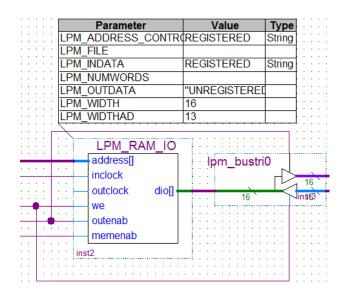

Figure 5.1.5 – Schematics of the "LPM\_RAM\_IO" function block with I/O driven by "lpm bustri0" function block

The virtual RAM module of firmware is based on standard parameterized RAM with a single I/O port generated from Altera LPM\_RAM\_IO Megafunction with data bus width (LPM\_WIDTH) parameter equal to 16 and address bus width (LPM\_WIDTHAD) parameter equal to 13. The single I/O port is driven by

parameterized tri-state buffer generated from lpm\_bustri Megafunction. Data-enable inputs of buffer are connected to the corresponding write enable and output enable signals from QuickUSB board as shown at figure 5.1.5. The LPM\_RAM\_IO RAM function block is used to simulate one memory block for SP\_RAM and one memory block for DP\_RAM in Internal RAM Simulator regime. This is realized by paging the virtual memory into two independent memory areas for SP\_RAM and DP\_RAM correspondingly. The two most significant bits of address input bus generated by "Addrincr" function block are used for the paging mechanism. Inclock input is fed by SEU chip 10MHz input clock, write enable (we) and output enable (outenab) input are fed by corresponding signals from the QuickUSB board and memory enable (memenab) input is fed by inverted cmd\_data signal to ensure that RAM is not accessed during command transfer phases.

Due to the fact that both internal and external 16 bit data bus pins are bidirectional the parameterized tri-state buffers generated from lpm\_bustri megafunction are used to drive them. Data-enable inputs of both buffers are connected to the corresponding write enable and output enable signals from QuickUSB board in a similar way to the shown at figure 5.1.5. Following the requirements of the SEU chip operation write enable and output enable signal going to chip are inverted. All other control signals for the SEU chip are initially generated inside the "Comminterpreter" function block in the required form described in appendix A.1.

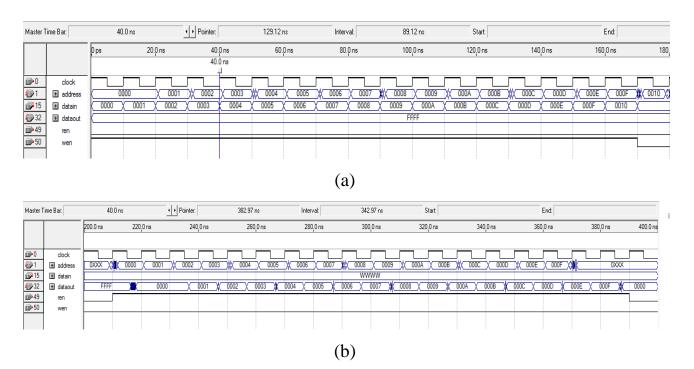

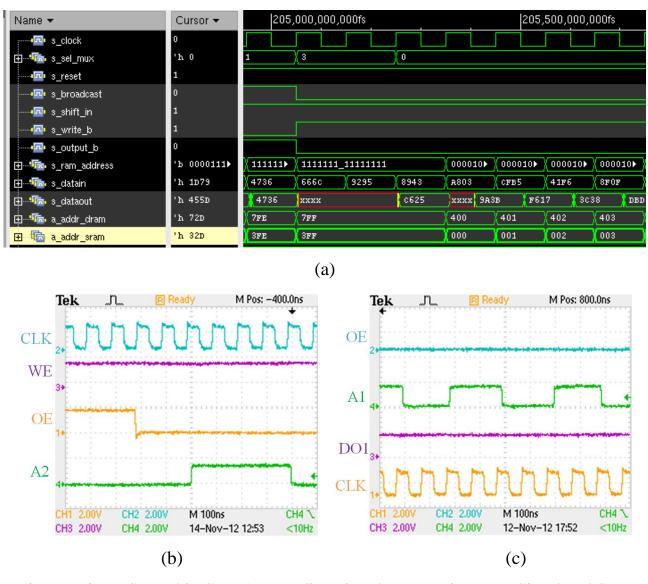

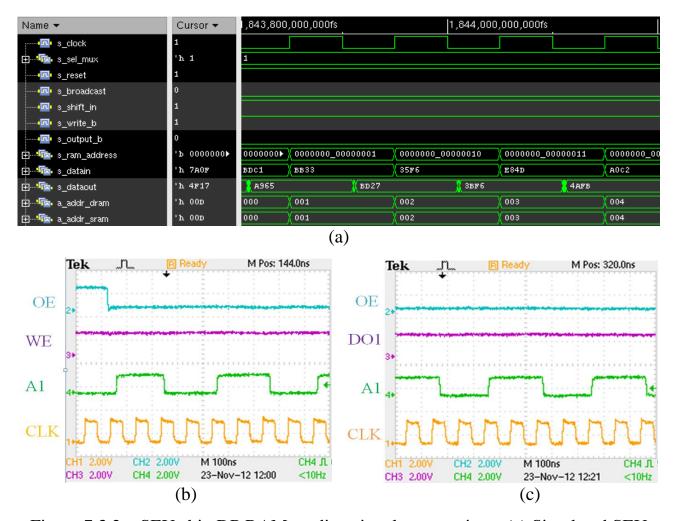

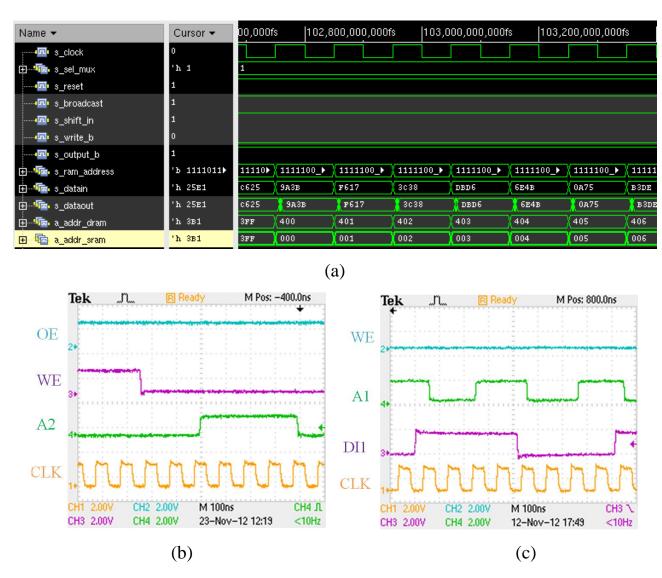

Despite the fact that the operation of the FPGA internal virtual memory was already proven by the real data acquisition with help of DAQ system, the results of the simulation of its operation are done with help of standard Quartus 2 Simulator and presented at figure 5.1.6. There clock signal stands for 10MHz clock important for the memory block operation which form is defined in the simulation settings file, but the proper operation with 48MHz clock from USB bus was also proved in normal (not Full Handshake) Quick-USB operation mode. Address signal stands for the regular 10bits address bus which values are defined in the simulation settings file.

Datain signal stands for the input data feeding the internal memory which values are defined in the simulation settings file, while dataout signal stands for the output data from the internal memory which values are calculated during the simulation. Ren signal stands for read (output) enable signal, allowing the memory to be read out, wen signal stands for write enable signal, allowing the memory to be written in – both signals are defined in the simulation settings file.

Figure 5.1.6 – Simulation results for internal FPGA memory:

(a) – writing process; (b) – reading process.

One can see from the afore presented figures, the data written to the memory during the reading process is successfully reproduced at the memory output during the reading process with exactly the same values that means that designed internal FPGA virtual memory is working properly.

Summarizing the aforementioned information, in this chapter we discussed the "SEU Test FPGA Firmware v 1.0" which downloaded to the FPGA module gives the possibility to interact with SEU chip from DAQ software. Two data transfer modes are used for it: the general data transfer allowing transferring the data to/from the memory and the command data transfer allowing transferring control commands intended for internal FPGA usage or for SEU chip operation. The two regimes of

firmware operation are implemented: the Internal RAM Simulator allowing testing the measurement setup while SEU chip is not presented using internal FPGA RAM and External RAM Connection allowing data exchange with SEU chip itself. The full schematic of developed firmware is presented in appendix B. Hereby the developed firmware allows operating the Digital DAQ FPGA module independently of SEU chip presence and provides the full range of features to communicate with SEU chip during the experiments.

#### **5.2 MCU Firmware**

The "SEU Test Atmega32 Firmware v 0.06" (ADAQ firmware) module was designed to be implemented with microcontroller unit (MCU) Atmega32 of DAQ board described in chapter 4.2. The module was developed in the BasCom software as compiled code designed in Basic programming language. The reason for choosing the BasCom compiler is that it provides the possibility of easy and robust development of the firmware for microcontrollers based on basic. This firmware is very important for the SEU measurement setup and it was developed by Dr. Vasilij Kushpil.

The developed firmware is designed to provide the possibility of analog data acquisition using ADAQ module. It fully promotes already declared feature of total separation of digital and analog data acquisition processes. ADAQ firmware provides easy and robust access to all the electronic modules of MCU itself and modules which are directly connected to and controlled by MCU. To provide the fast access to ADAQ module the communication via RS-232 interface is done at a 9600 baud rate. Due to the fact that MCU is connected with PC via RS-232 interface, all the used controlling commands are written in a simplified way, so the user can easily use any simple terminal software to achieve access to MCU module. For regular ADAQ operation and visual control of important parameters it is possible to use the general

DAQ or specialized ADAQ software described in chapter 6.1 and 6.2 correspondingly. Detailed schematic of ADAQ firmware is presented at figure 5.2.1.

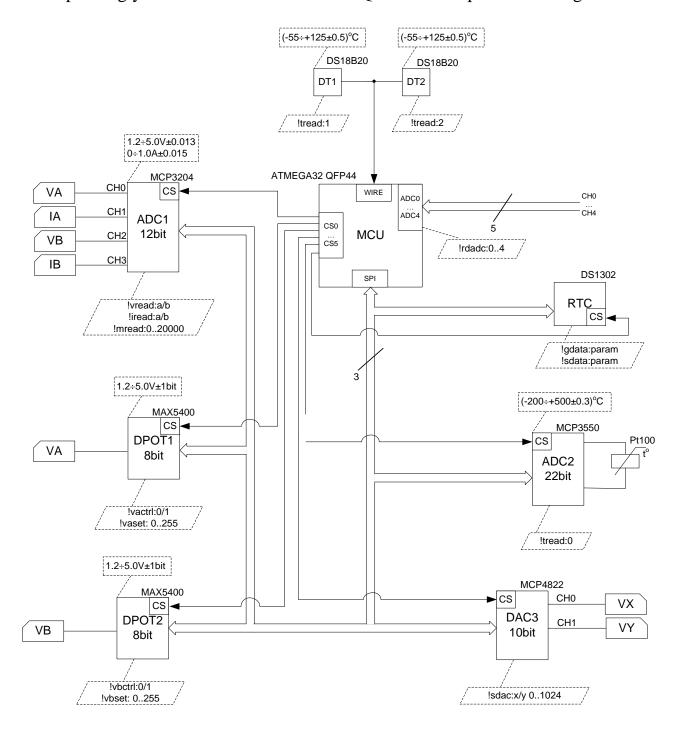

Figure 5.2.1 – Schematics of the ADAQ functional modules connection with MCU, corresponding commands and parameters limitations

Each module controlled by the MCU has its own purpose and operating command defined in the ADAQ firmware. Every command starts with "!" symbol that indicates that MCU should consider the transferred data as a command. All the

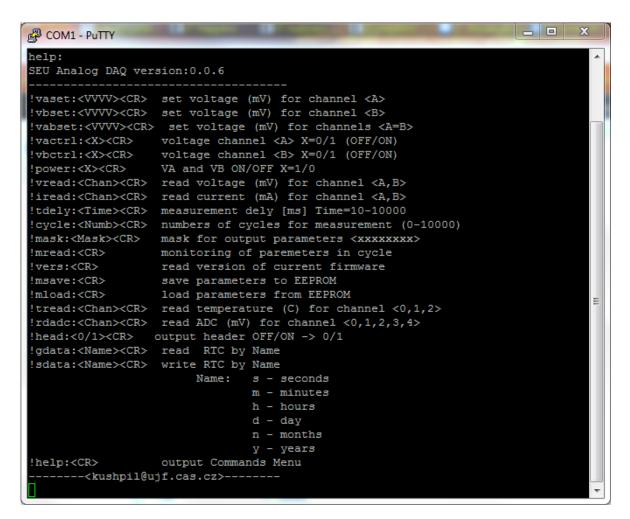

commands have simple and intuitive spelling to provide easy usage. To provide the easier operation with developed firmware the "!help:" command prints all the used commands with the short description. The "!vers:" command or simple pressing the spacebar key shows the current firmware version. The "!msave:" and "!mload:" commands allow to save the other commands parameters such as desired voltages values to EEPROM memory inside the MCU and load them from it after the next connection procedure. The result of processing the "!help:" command is represented at figure 5.2.2.

Figure 5.2.2 – The result of processing of "!help" command using the terminal "PUTTY" for the connection

The 12bit analog digital converter ADC1 module (MCP3204 chip) provides the possibility to measure general power supply parameters, such as voltage in channel A (VA), voltage in channel B (VB), current in channel A (IA) and current in channel B (IB). These values can be measured with the help of three different

commands: "!vread:x", "!iread:x" and "!mread:x". The "!vread:x" command allows to process single measurement of the voltage level in millivolts at the channel A or at channel B and in each case "x" symbol should be replaced by "a" or "b" symbol correspondingly. These voltage levels can be measured in ranges from 1.2 to 5.0V with maximal statistical error of 0.013V. The voltage range is defined by the voltage setting range of digital potentiometers DPOT1 and DPOT2 while statistical error is defined by regular voltage measuring noise.

The "!iread:x" command allows to process single measurement of the current at the channel A or at channel B in milliamperes and in each case "x" symbol should be replaced by "a" or "b" symbol correspondingly. These currents can be measured in ranges from 0 to 1.0A with maximal statistical error of 0.015V. The current measuring range is defined by the possible range of power supply currents while statistical error is defined by regular current noise.